GATE PRACTICE PROBLEM ON BJT - 1

In this circuit, the 10nF capacitor is initially charged to 5V. The NPN transistor is driven with a 40 micro-sec period rectangular wave going from 0 to 3.7 V and an ON duration of Ton. Determine Ton so that the transistors never leave the active region even after an arbitrarily long time. NPN and PNP transistors are active with Vbe= 0.7 V and Veb= 0.7V respectively.

Solution: This is our 2nd problem on "GATE Revision". For the first problem check index.

There are two phases -----------

Phase-I: capacitor is discharged by a constant current

of 0.6 mA. (both transistors are on)

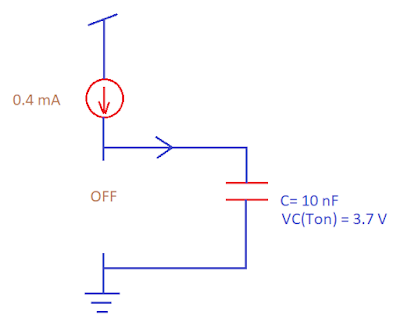

Phase-II: The capacitor is charged by a constant current of 0.4

mA.(only pnp is on)

Consider,

Phase-I: Voltage across the

capacitor is decreased by Vx (from the time t= 0 to t=Ton)

Phase-II: Voltage across the capacitor is increased by Vy (from

the time t=Ton to t=T )

First cycle

t=0, Vc(0) = 5 ;

t=Ton, Vc(Ton) = 5-x ;

t=T, Vc(T) = 5-x+y ;

Second Cycle

t=T+Ton, Vc(T+Ton) = 5-2x+yt=T, Vc(T) = 5-x+y;

t=2T, Vc(2T) = 5-2x+2y

If you observe, at the end of each cycle Capacitor voltage is increased by y-x

if y > x - Vc will rise with each cycle pass. When Vc > 7.3 V, pnp goes into saturation.

if x > y - Vc will fall with each cycle pass. When Vc < 3.7 V, npn goes into saturation.

the option left is x=y.

\[\frac{I_{dischage}}{C}\times T_{on} = \frac{I_{charge}}{C}\times (T-T_{on})\]

\[=>I_{dischage}\times T_{on} = I_{charge}\times (T-T_{on})\]

\[=>(I_{dischage}+I_{dischage}) \times T_{on} = I_{chage}\times T\]

\[=>T_{on} = T\times \frac{I_{charge}}{(I_{dischage}+I_{dischage})}\]

\[=>T_{on} = 40\times \frac{0.4 \, mA}{(0.4 \, mA + 0.6\, mA)} \: \mu sec\]

\[=>T_{on} = 16 \: \mu sec\]

No comments:

Post a Comment